22/02/1999

For at kunne designe funktionelle digitale kredsløb i VHDL er det ikke nok blot at definere enheder (entities) og arkitekturer. Vi har brug for et sprogværktøj til at beskrive den faktiske adfærd af vores kredsløb. Her kommer VHDL's operatorer og samtidige statements ind i billedet. De er grundstenene, der giver os mulighed for at modellere alt fra simple logiske porte til komplekse systemer. Uden dem ville vi kun kunne definere input- og output-porte uden nogen intern logik.

Digitale kredsløb kan overordnet inddeles i to hovedkategorier: kombinatorisk logik og sekventiel logik. Kombinatorisk logik består primært af grundlæggende logiske porte som AND, OR og NOT. Når input til et sådant kredsløb ændres, ændres outputtet næsten øjeblikkeligt, kun forsinket af signalets udbredelsestid gennem portene. I modsætning hertil bruger sekventiel logik et kloksignal og hukommelseselementer som flip-flops. Her er outputændringer synkroniseret med kloksignalet og sker ikke øjeblikkeligt. Denne artikel fokuserer primært på modellering af kombinatorisk logik.

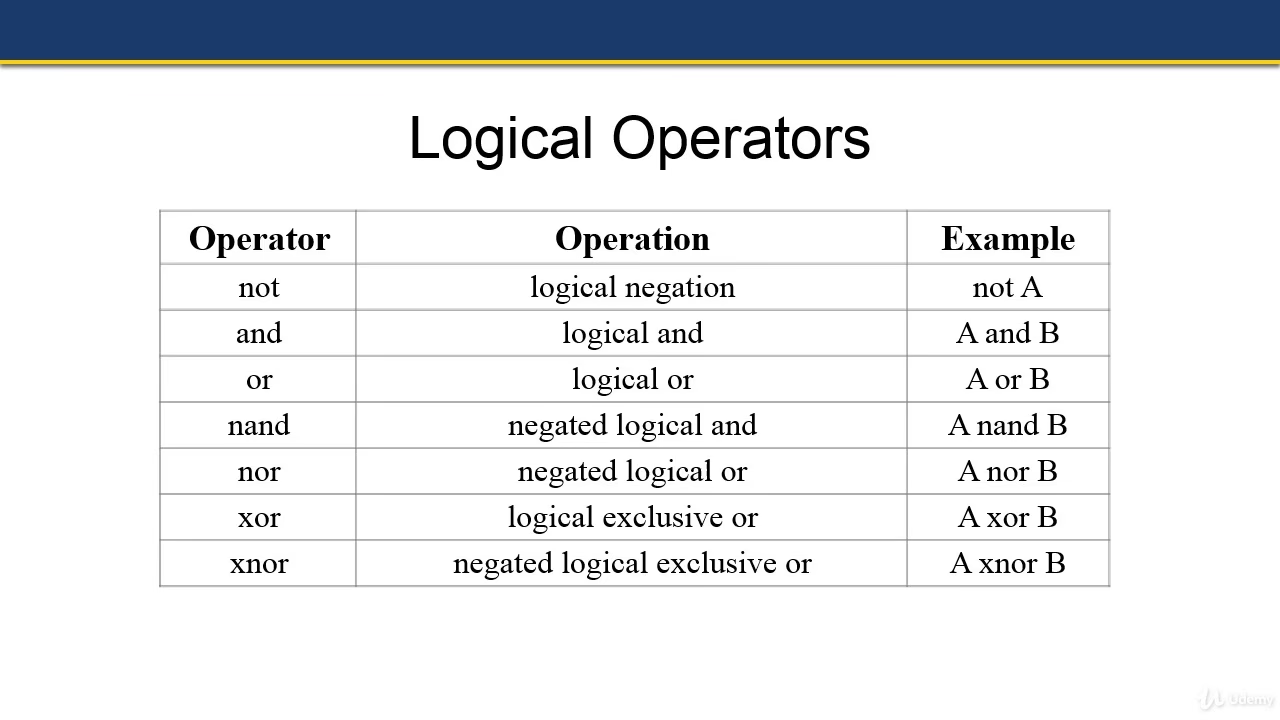

Grundlæggende Logiske Operatorer i VHDL

De simpleste elementer at modellere i VHDL er de grundlæggende logiske porte. Hver af disse porte har en tilsvarende operator i sproget. Samlet set er disse kendt som logiske operatorer. De inkluderer:

- AND

- OR

- NAND

- NOR

- XOR

- NOT

For at illustrere dette kan vi betragte en simpel to-input AND-port. VHDL-koden nedenfor bruger den logiske AND-operator til at implementere dette kredsløb.

and_out <= a and b;Selvom koden er simpel, er der et par vigtige koncepter at bemærke. Det første er VHDL's tildelingsoperator (<=), som skal bruges til alle signaler. Denne svarer groft til = operatoren i de fleste andre programmeringssprog. Det er vigtigt at skelne den fra tildelingsoperatoren for variable (:=), som kun bruges inde i processer. Datatypen for de signaler, der anvendes, er også afgørende. Logiske operatorer fungerer typisk med typer som std_logic eller std_logic_vector, men ikke med skalære typer som integer eller real.

Funktionaliteten kan let ændres ved at udskifte operatoren. Nedenfor er et eksempel på en tre-input XOR-port:

xor_out <= a xor b xor c;NOT-operatoren er unik, da den kun har ét input. Syntaksen er som følger:

not_out <= not a;Kombination af Logiske Operatorer

I praksis består kombinatoriske kredsløb næsten altid af mere end én type logisk port. VHDL giver os mulighed for at blande logiske operatorer for at skabe modeller af mere komplekse kredsløb. Lad os se på et kredsløb med en AND-port og en OR-port.

Koden nedenfor implementerer dette kredsløb ved hjælp af VHDL:

logic_out <= (A and B) or C;Denne kode er let at forstå, da den bygger på de operatorer, vi allerede har diskuteret. Det er dog afgørende at bruge parenteser, når man modellerer kredsløb med flere logiske porte. Parenteser sikrer ikke kun, at designet fungerer som forventet ved at styre operationsrækkefølgen, men de gør også koden meget lettere at læse og forstå for andre udviklere.

Modellering af Multiplexere (Mux) i VHDL

Ud over simple logiske porte er multiplexere (ofte forkortet til 'mux') en meget almindelig komponent i kombinatoriske digitale kredsløb. En multiplexer vælger ét af flere input-signaler og sender det valgte signal videre til et enkelt output. Valget styres af et eller flere kontrolsignaler. I VHDL findes der to primære samtidige statements, som vi kan bruge til at modellere en mux: with select og when else.

VHDL 'With Select' Statementet

Når vi bruger with select-statementet i et VHDL-design, kan vi tildele forskellige værdier til et signal baseret på værdien af et andet kontrolsignal. Dette er sandsynligvis den mest intuitive måde at modellere en mux på i VHDL.

Den grundlæggende syntaks for with select-statementet er vist nedenfor:

with <kontrolsignal> select <output_signal> <= <værdi_a> when <valg1>, <værdi_b> when <valg2>, <værdi_c> when others;Her tildeles <output_signal> en værdi baseret på værdien af <kontrolsignal>. For eksempel, hvis <kontrolsignal> er lig med <valg1>, tildeles <værdi_a> til outputtet. when others-klausulen bruges til at dække alle andre mulige værdier af kontrolsignalet, som ikke er eksplicit nævnt. Dette er god praksis for at undgå utilsigtede latches i syntesen.

Lad os tage et praktisk eksempel med en fire-til-en multiplexer. Outputtet q sættes til et af de fire inputs (a, b, c eller d) afhængigt af værdien af det 2-bit kontrolsignal addr.

with addr select q <= a when "00", b when "01", c when "10", d when others;VHDL 'When Else' Statementet

Den anden metode, vi kan bruge, er when else-statementet. Her tildeler vi forskellige værdier til et signal baseret på en række sandhedsværdier (boolean expressions). Vi skriver et separat udtryk for hver af de værdier, der kan tildeles signalet. Når en af disse betingelser evalueres til sand, tildeles signalet den værdi, der er forbundet med betingelsen.

Den grundlæggende syntaks for when else-statementet ser således ud:

<output_signal> <= <værdi_a> when <betingelse1> else <værdi_b> when <betingelse2> else <værdi_c>;Hvis <betingelse1> er sand, tildeles <værdi_a> til <output_signal>. Hvis den er falsk, evalueres den næste betingelse. Det sidste else uden en when fanger alle resterende tilfælde, hvor ingen af de foregående betingelser var sande.

Hvis vi igen ser på vores fire-til-en multiplexer, kan den implementeres med when else som vist nedenfor:

q <= a when addr = "00" else b when addr = "01" else c when addr = "10" else d;Sammenligning af Mux-Modelleringsteknikker

Teknisk set udfører with select og when else den samme funktion, og i næsten alle tilfælde vil de give identiske synteseresultater. Valget mellem dem er ofte et spørgsmål om stil og læsbarhed. Der er dog en vigtig forskel i deres fleksibilitet.

with select kan kun bruge et enkelt signal til at bestemme, hvilken data der skal tildeles. I modsætning hertil kan when else inkludere komplekse logiske udtryk i sine betingelser. Dette betyder, at man ofte kan skrive mere kompakt VHDL-kode ved at bruge when else, især når kontrolsignalet er resultatet af en logisk operation.

| Egenskab | With Select | When Else |

|---|---|---|

| Selektion baseret på | Værdien af et enkelt signal | Logiske udtryk (boolean expressions) |

| Fleksibilitet | Begrænset til ét kontrolsignal | Høj, kan inkludere kompleks logik |

| Læsbarhed | Meget høj for simple multiplexere | Høj, kan være mere kompakt for komplekse betingelser |

Instansiering af Komponenter i VHDL

Indtil nu har vi vist, hvordan man kan bruge VHDL til at beskrive adfærden af simple kredsløb. En anden fundamental teknik er at forbinde flere tidligere definerede VHDL entity-arkitektur-par for at bygge et mere komplekst kredsløb. Dette kaldes instansiering og svarer til at forbinde fysiske elektroniske komponenter på et printkort. Der er to metoder til dette i VHDL: komponentinstansiering og direkte entitetsinstansiering.

VHDL Komponentinstansiering

Når man bruger komponentinstansiering, skal man først definere en komponent, før den kan bruges. Dette gøres typisk i den deklarative del af arkitekturen, ligesom man ville erklære et signal.

Komponenterklæringen skal matche navnet og portene på den oprindelige entity. Efter at have erklæret komponenten, kan vi instansiere den i arkitekturen ved hjælp af et port map, som forbinder komponentens porte til signaler i den nuværende arkitektur.

-- 1. Komponenterklæring component <komponent_navn> is port ( <port_navn1>: <mode> <signal_type> ); end component <komponent_navn>; -- 2. Instansiering <instans_navn>: component <komponent_navn> port map ( <port_navn1> => <signal_navn1>, <port_navn2> => <signal_navn2> );Hvis en output-port på komponenten ikke skal bruges, kan man bruge nøgleordet open til at angive, at den ikke er forbundet.

VHDL Direkte Entitetsinstansiering

Den anden metode er direkte entitetsinstansiering. Med denne metode kan vi direkte forbinde en entity i et nyt design uden først at skulle erklære en komponent. Dette kan gøre koden mere kompakt.

<instans_navn>: entity <biblioteks_navn>.<komponent_navn>(<arkitektur_navn>) port map ( <port_navn1> => <signal_navn1>, <port_navn2> => <signal_navn2> );Med denne metode skal vi eksplicit angive navnet på både biblioteket (f.eks. work) og arkitekturen, vi vil bruge. Port map-delen fungerer på nøjagtig samme måde som ved komponentinstansiering.

Ofte Stillede Spørgsmål

Hvilke datatyper kan ikke bruges med VHDL's logiske operatorer?

Skalære typer som integer og real kan ikke bruges direkte med logiske operatorer som AND og OR. Disse operatorer er designet til at fungere på bit-baserede typer som bit, std_logic, og vektorer af disse typer.

Hvordan skriver man koden for en 4-input NAND-gate?

En 4-input NAND-gate kan implementeres i en enkelt linje ved hjælp af NAND-operatoren:

nand_out <= a nand b nand c nand d;Hvilke to statements kan bruges til at modellere multiplexere i VHDL?

De to primære samtidige statements til at modellere multiplexere er with select-statementet (også kendt som selected signal assignment) og when else-statementet (også kendt som conditional signal assignment).

Kan du give et eksempel på en 8-input multiplexer med begge metoder?

Absolut. Her er en 8-til-1 multiplexer, hvor kontrolsignalet sel er en 3-bit std_logic_vector.

Med 'with select' statementet:

with sel select mux_out <= a when "000", b when "001", c when "010", d when "011", e when "100", f when "101", g when "110", h when others;Med 'when else' statementet:

mux_out <= a when sel = "000" else b when sel = "001" else c when sel = "010" else d when sel = "011" else e when sel = "100" else f when sel = "101" else g when sel = "110" else h;Hvis du vil læse andre artikler, der ligner VHDL Operatorer og Statements Forklaret, kan du besøge kategorien Teknologi.